Lenovo AD80582QH056003 Datenblatt Seite 39

- Seite / 136

- Inhaltsverzeichnis

- LESEZEICHEN

Bewertet. / 5. Basierend auf Kundenbewertungen

Intel® Xeon® Processor 7400 Series Datasheet 39

Electrical Specifications

13. This specification applies only to DSTBN[3:0]# and is measured to the second falling edge of the strobe.

14. This specification reflects a typical value, not a minimum or maximum.

15. For this timing parameter, n = 0 to 1.

Notes:

1. Unless otherwise noted, all specifications in this table apply to all processor frequencies.

2. All AC timings for the Asynchronous GTL+ signals are referenced to the BCLK0 rising edge at Crossing

Voltage (V

CROSS

). PWRGOOD is referenced to BCLK0 rising edge at 0.5 * V

TT

.

3. These signals may be driven asynchronously.

4. Refer to Section 7.2 for additional timing requirements for entering and leaving low power states.

5. A minimum pulse width of 500 µs is recommended when FORCEPR# is asserted by the system.

6. Refer to the PWRGOOD signal definition in Section 5 for more details information on behavior of the signal.

7. Length of assertion for PROCHOT# does not equal TCC activation time. Time is required after the assertion

and before the deassertion of PROCHOT# for the processor to enable or disable the TCC.

8. Intel recommends the V

TT

power supply also be removed upon assertion of THERMTRIP#.

9. This specification requires that the VID and BSEL signals be sampled no earlier than 10 μs after V

CC

(at

V

CC_BOOT

voltage) and V

TT

are stable.

10. Parameter must be measured after applicable voltage level is stable. “Stable” means that the power supply

is in regulation as defined by the minimum and maximum DC/AC specifications for all components being

powered by it.

11. The maximum PWRGOOD rise time specification denotes the slowest allowable rise time for the processor.

Measured between (0.3* V

TT

) and (0.7*V

TT

).

12. See Table 2-19 for BCLK specifications.

Notes:

1. Before the clock that de-asserts RESET#.

2. After the clock that de-asserts RESET#.

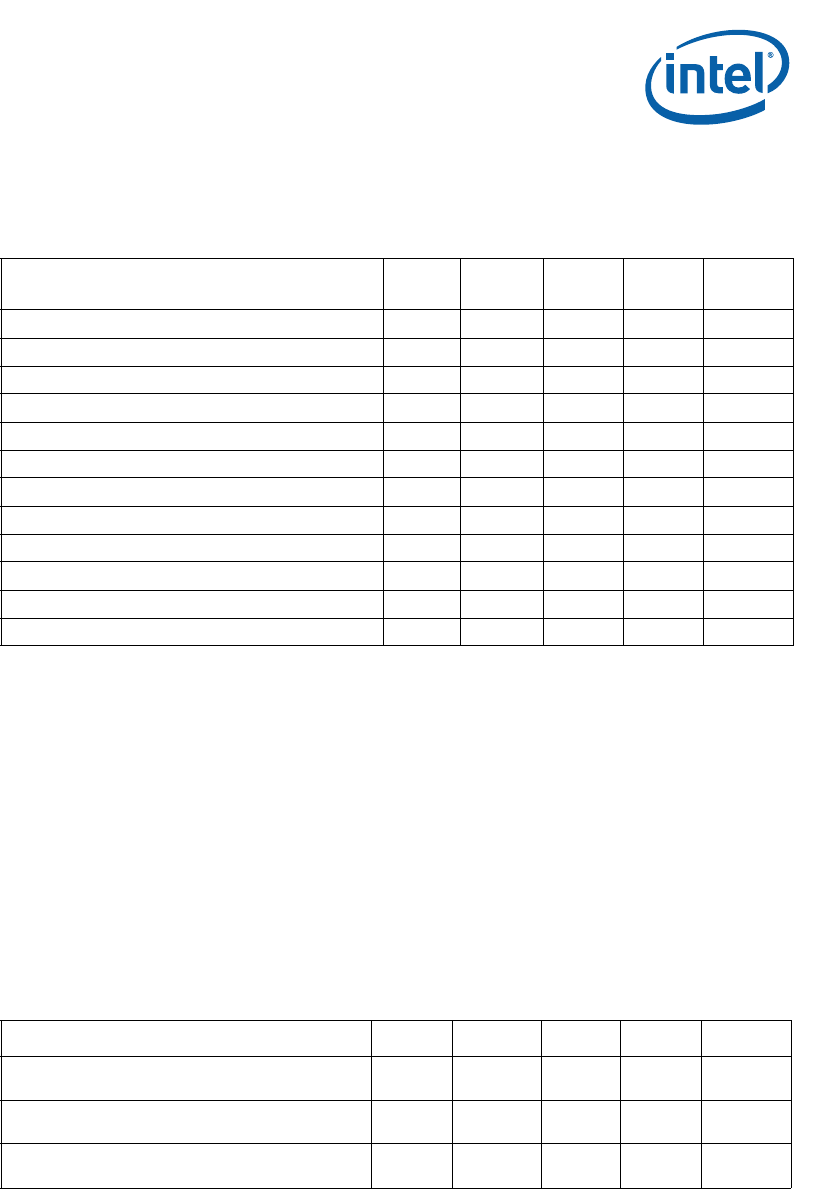

Table 2-22. Miscellaneous GTL+ AC Specifications

T# Parameter Min Max Unit Figure

Notes

1, 2, 3, 4

T35: Asynchronous GTL+ input pulse width 8 BCLKs 5

T36: PWRGOOD assertion to RESET# de-assertion 1 10 ms 2-20

T37: BCLK stable to PWRGOOD assertion 10 BCLKs 2-20 6,12

T38: PROCHOT# pulse width 500 µs 2-16 7

T39: THERMTRIP# assertion until V

CC

removed 500 ms 2-17 8

T40: FERR# valid delay from STPCLK# deassertion 0 5 BCLKs 2-21

T41: V

CC

stable to PWRGOOD assertion 0.05 500 ms 2-20 10

T42: PWRGOOD rise time 20 ns 11

T43: V

CC_BOOT

stable to VID / BSEL valid 10 µs 2-20 9,10

T44: VID / BSEL valid to V

CC

stable 100 µs 2-20 10

T48: V

TT

stable to VID / BSEL valid 10 µs 2-20 10

T49: V

CCPLL

stable to PWRGOOD assertion 1 ms 2-20 10

Table 2-23. Front Side Bus AC Specifications (Reset Conditions)

T# Parameter Min Max Unit Figure Notes

T45: Reset Configuration Signals

(A[39:3]#, BR[1:0]#, INIT#, SMI#) Setup Time

480 µs 2-20 1

T46: Reset Configuration Signals

(A[39:3]#, INIT#, SMI#) Hold Time

220BCLKs2-20 2

T47: Reset Configuration Signals

BR[1:0]# Hold Time

22BCLKs2-20 2

- Datasheet 1

- Contents 3

- Revision History 7

- 1 Introduction 9

- 1.1 Terminology 11

- Introduction 12

- 1.2 State of Data 13

- 1.3 References 13

- 2 Electrical Specifications 15

- 2.2 Decoupling Guidelines 16

- Clocking 16

- 2.3.2 PLL Power Supply 18

- Electrical Specifications 20

- Table 2-4. FSB Signal Groups 21

- Asynchronous Signals 22

- 2.9 Mixing Processors 23

- Time Duration (s) 28

- Sustained Current (A) 28

- Table 2-10. V 30

- Figure 2-4. V 31

- 2.11.2 V 33

- Overshoot Specification 33

- 2.11.3 Die Voltage Validation 33

- 2.11.4.1 DC Characteristics 34

- 2.12 AGTL+ FSB Specifications 35

- Tp = T1: BCLK[1:0] period 42

- THERMTRIP# 46

- System bus 48

- FERR#/PBE# 48

- Figure 2-22. VID Step Timings 49

- 3 Mechanical Specifications 51

- Mechanical Specifications 52

- 3.7 Processor Materials 61

- 3.8 Processor Markings 62

- Processor 63

- 4 Pin Listing 65

- (Sheet 3 of 16) 66

- (Sheet 4 of 16) 66

- (Sheet 5 of 16) 67

- (Sheet 6 of 16) 67

- (Sheet 7 of 16) 68

- (Sheet 8 of 16) 68

- (Sheet 9 of 16) 69

- (Sheet 10 of 16) 69

- (Sheet 11 of 16) 70

- (Sheet 12 of 16) 70

- (Sheet 13 of 16) 71

- (Sheet 14 of 16) 71

- (Sheet 15 of 16) 72

- (Sheet 16 of 16) 72

- (Sheet 1 of 14) 73

- (Sheet 2 of 14) 73

- (Sheet 3 of 14) 74

- (Sheet 4 of 14) 74

- (Sheet 5 of 14) 75

- (Sheet 6 of 14) 75

- (Sheet 7 of 14) 76

- (Sheet 8 of 14) 76

- (Sheet 9 of 14) 77

- (Sheet 10 of 14) 77

- (Sheet 11 of 14) 78

- (Sheet 12 of 14) 78

- (Sheet 13 of 14) 79

- (Sheet 14 of 14) 79

- Pin Listing 80

- 5 Signal Definitions 81

- FSB agents 85

- . The processor includes 86

- 6 Thermal Specifications 89

- CASE_MAX 90

- CASE (°C) 91

- = 0.431 x Power + 45 95

- Power (W) 96

- Temperature (C) 96

- 6.1.2 Thermal Metrology 97

- 6.2.2 Intel Thermal Monitor 97

- 6.2.3 Intel Thermal Monitor 2 98

- 6.2.4 On-Demand Mode 99

- 6.2.5 PROCHOT# Signal 100

- 6.2.6 FORCEPR# Signal 100

- 6.2.7 THERMTRIP# Signal 100

- 6.3.1 Introduction 101

- 6.3.1.1 T 102

- 6.3.2.1 PECI Device Address 103

- 6.3.2.2 PECI Command Support 103

- 7 Features 105

- 7.2.2.1 HALT State 106

- 7.2.2.2 Extended HALT State 106

- 7.2.3 Stop-Grant State 108

- 7.3 Enhanced Intel SpeedStep 109

- Technology 109

- Features 110

- 7.4.1 SMBus Device Addressing 111

- Transactions 112

- 7.4.3.1 Header 115

- 7.4.3.2 Processor Data 119

- 0Eh-13h 120

- 7.4.3.3 Processor Core Data 121

- Offset: 1Ah-1Bh 122

- 7.4.3.4 Cache Data 124

- Offset: 29h-2Ah 125

- 2Bh-2Ch 125

- 2Dh-2Eh 125

- 7.4.3.5 Package Data 126

- 7.4.3.6 Part Number Data 127

- 38h-3Eh 128

- 3Fh-4Ch 128

- 4Dh=54h 128

- 55h-6Eh 128

- 71h-72h 129

- 7.4.3.8 Feature Data 130

- 7.4.3.9 OD: Other Data 131

- 7.4.4 Checksums 132

- 7.4.5 Scratch EEPROM 132

- 8 Debug Tools Specifications 133

- Debug Tools Specifications 134

- 9.1 Introduction 135

- 9.2 Thermal Specifications 135

Kommentare zu diesen Handbüchern