Lenovo AD80582QH056003 Datenblatt Seite 49

- Seite / 136

- Inhaltsverzeichnis

- LESEZEICHEN

Bewertet. / 5. Basierend auf Kundenbewertungen

Intel® Xeon® Processor 7400 Series Datasheet 49

Electrical Specifications

Notes:

1. Ta = T40 (FERR# Valid Delay from STPCLK# Deassertion).

2. FERR# / PBE# is undefined from STPCLK# assertion until the Stop-Grant acknowledge is driven on the

FSB. FERR# / PBE# is also undefined for a period of Ta from STPCLK# deassertion. Inside these undefined

regions, the PBE# signal is driven. FERR# is driven at all other times.

§

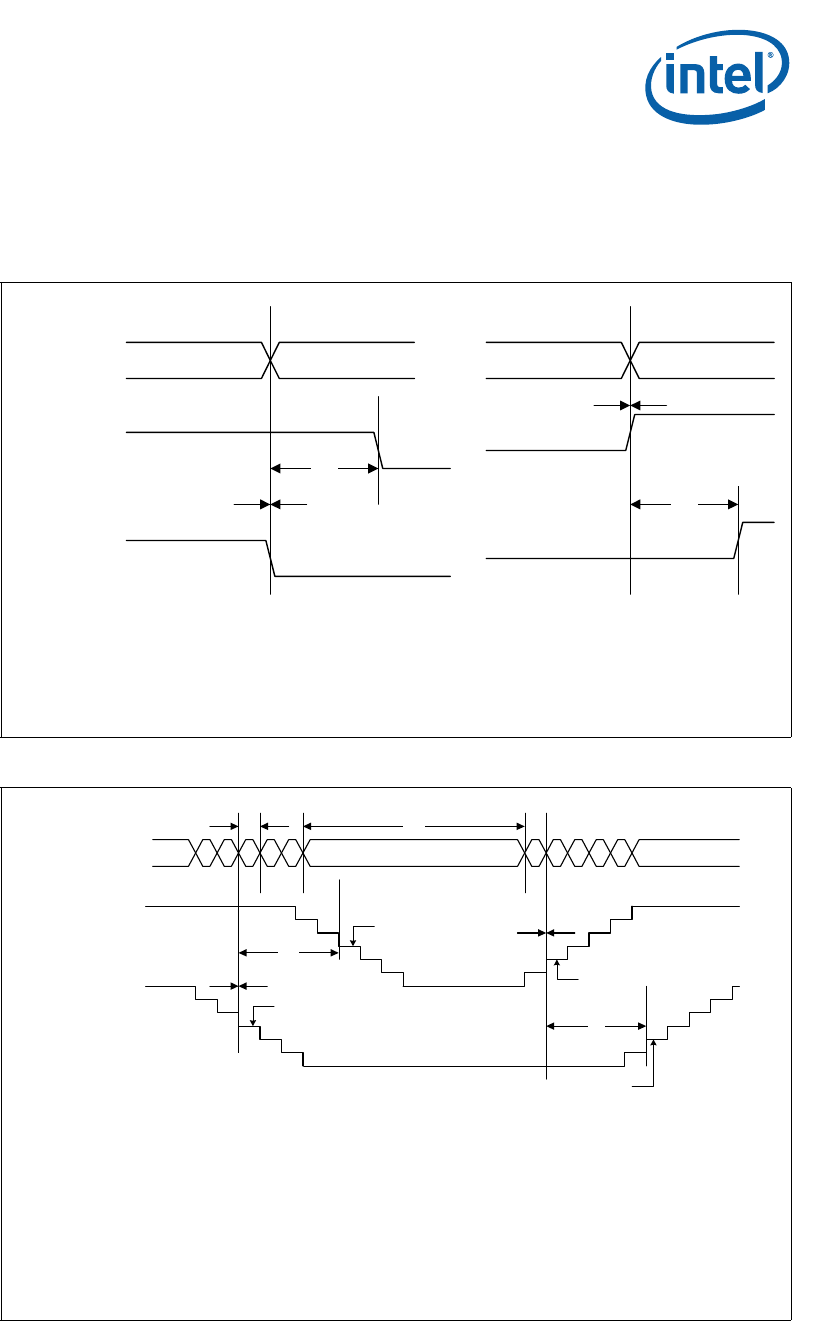

Figure 2-22. VID Step Timings

Figure 2-23. VID Step Times and Vcc Waveforms

VID

n n-1 m+1m

...

Ta

Tb

Tc

Td

Ta = T84: VID Down to Valid V

CC

(max)

Tb = T82: VID Down to Valid V

CC

(min)

Tc = T85: VID Up to Valid V

CC

(max)

Td = T83: VID Up to Valid V

CC

(min)

V

CC

(max)

V

CC

(min)

VID

V

CC

(max)

V

CC

(min)

n

n-1

n-2

n-3

n-4

n-6 = VID

TM2

n-1

n-2

n-3

n-4

n

Ta Tb

Td

Tc

Te

Tf

V

CC

(max,n-3)

V

CC

(min,n-3)

V

CC

(max,n-4)

V

CC

(min,n-4)

Ta = T80: VID Step Time

Tb = T81: Thermal Monitor 2 Dwell Time

Tc = T84: VID Down to Valid V

CC

(max)

Td = T82: VID Down to Valid V

CC

(min)

Te = T85: VID Up to Valid V

CC

(max)

Tf = T83: VID Up to Valid V

CC

(min)

n-5

n-5

Note: This waveform illustrates an example of an Intel Thermal

Monitor 2 transition or an Intel Enhanced SpeedStep

Technology transition that is six VID steps down from the

current state and six steps back up. Any arbitrary up or down

transition can be generalized from this waveform.

- Datasheet 1

- Contents 3

- Revision History 7

- 1 Introduction 9

- 1.1 Terminology 11

- Introduction 12

- 1.2 State of Data 13

- 1.3 References 13

- 2 Electrical Specifications 15

- 2.2 Decoupling Guidelines 16

- Clocking 16

- 2.3.2 PLL Power Supply 18

- Electrical Specifications 20

- Table 2-4. FSB Signal Groups 21

- Asynchronous Signals 22

- 2.9 Mixing Processors 23

- Time Duration (s) 28

- Sustained Current (A) 28

- Table 2-10. V 30

- Figure 2-4. V 31

- 2.11.2 V 33

- Overshoot Specification 33

- 2.11.3 Die Voltage Validation 33

- 2.11.4.1 DC Characteristics 34

- 2.12 AGTL+ FSB Specifications 35

- Tp = T1: BCLK[1:0] period 42

- THERMTRIP# 46

- System bus 48

- FERR#/PBE# 48

- Figure 2-22. VID Step Timings 49

- 3 Mechanical Specifications 51

- Mechanical Specifications 52

- 3.7 Processor Materials 61

- 3.8 Processor Markings 62

- Processor 63

- 4 Pin Listing 65

- (Sheet 3 of 16) 66

- (Sheet 4 of 16) 66

- (Sheet 5 of 16) 67

- (Sheet 6 of 16) 67

- (Sheet 7 of 16) 68

- (Sheet 8 of 16) 68

- (Sheet 9 of 16) 69

- (Sheet 10 of 16) 69

- (Sheet 11 of 16) 70

- (Sheet 12 of 16) 70

- (Sheet 13 of 16) 71

- (Sheet 14 of 16) 71

- (Sheet 15 of 16) 72

- (Sheet 16 of 16) 72

- (Sheet 1 of 14) 73

- (Sheet 2 of 14) 73

- (Sheet 3 of 14) 74

- (Sheet 4 of 14) 74

- (Sheet 5 of 14) 75

- (Sheet 6 of 14) 75

- (Sheet 7 of 14) 76

- (Sheet 8 of 14) 76

- (Sheet 9 of 14) 77

- (Sheet 10 of 14) 77

- (Sheet 11 of 14) 78

- (Sheet 12 of 14) 78

- (Sheet 13 of 14) 79

- (Sheet 14 of 14) 79

- Pin Listing 80

- 5 Signal Definitions 81

- FSB agents 85

- . The processor includes 86

- 6 Thermal Specifications 89

- CASE_MAX 90

- CASE (°C) 91

- = 0.431 x Power + 45 95

- Power (W) 96

- Temperature (C) 96

- 6.1.2 Thermal Metrology 97

- 6.2.2 Intel Thermal Monitor 97

- 6.2.3 Intel Thermal Monitor 2 98

- 6.2.4 On-Demand Mode 99

- 6.2.5 PROCHOT# Signal 100

- 6.2.6 FORCEPR# Signal 100

- 6.2.7 THERMTRIP# Signal 100

- 6.3.1 Introduction 101

- 6.3.1.1 T 102

- 6.3.2.1 PECI Device Address 103

- 6.3.2.2 PECI Command Support 103

- 7 Features 105

- 7.2.2.1 HALT State 106

- 7.2.2.2 Extended HALT State 106

- 7.2.3 Stop-Grant State 108

- 7.3 Enhanced Intel SpeedStep 109

- Technology 109

- Features 110

- 7.4.1 SMBus Device Addressing 111

- Transactions 112

- 7.4.3.1 Header 115

- 7.4.3.2 Processor Data 119

- 0Eh-13h 120

- 7.4.3.3 Processor Core Data 121

- Offset: 1Ah-1Bh 122

- 7.4.3.4 Cache Data 124

- Offset: 29h-2Ah 125

- 2Bh-2Ch 125

- 2Dh-2Eh 125

- 7.4.3.5 Package Data 126

- 7.4.3.6 Part Number Data 127

- 38h-3Eh 128

- 3Fh-4Ch 128

- 4Dh=54h 128

- 55h-6Eh 128

- 71h-72h 129

- 7.4.3.8 Feature Data 130

- 7.4.3.9 OD: Other Data 131

- 7.4.4 Checksums 132

- 7.4.5 Scratch EEPROM 132

- 8 Debug Tools Specifications 133

- Debug Tools Specifications 134

- 9.1 Introduction 135

- 9.2 Thermal Specifications 135

Kommentare zu diesen Handbüchern