Lenovo LF80565QH0254M Datenblatt Seite 39

- Seite / 142

- Inhaltsverzeichnis

- LESEZEICHEN

Bewertet. / 5. Basierend auf Kundenbewertungen

Document Number: 318080-002 39

Electrical Specifications

Notes:

1. Unless otherwise noted, all specifications in this table apply to all processor frequencies.

2. The tolerances for this specification have been stated generically to enable system designer to calculate the minimum values

across the range of V

TT

.

3. GTLREF_DATA_MID, GTLREF_DATA_END, GTLREF_ADD_MID, and GTLREF_ADD_END is generated from V

TT

on the

baseboard by a voltage divider of 1% resistors. The minimum and maximum specifications account for this resistor tolerance.

Refer to the appropriate platform design guidelines for implementation details. The V

TT

referred to in these specifications is

the instantaneous V

TT

.

4. R

TT

is the on-die termination resistance measured at V

OL

of the AGTL+ output driver. Measured at 0.31*V

TT

. R

TT

is connected

to V

TT

on die. Refer to processor I/O Buffer Models for I/V characteristics.

5. COMP resistance must be provided on the system board with +/- 1% resistors. See the applicable platform design guide for

implementation details.

Notes:

1. Unless otherwise noted, all specifications in this table apply to all processor frequencies.

2. Crossing Voltage is defined as the instantaneous voltage value when the rising edge of BCLK0 is equal to the falling edge of

BCLK1.

3. V

Havg

is the statistical average of the V

H

measured by the oscilloscope.

4. Overshoot is defined as the absolute value of the maximum voltage.

5. Undershoot is defined as the absolute value of the minimum voltage.

6. Ringback Margin is defined as the absolute voltage difference between the maximum Rising Edge Ringback and the maximum

Falling Edge Ringback.

7. Threshold Region is defined as a region entered around the crossing point voltage in which the differential receiver switches.

It includes input threshold hysteresis.

8. The crossing point must meet the absolute and relative crossing point specifications simultaneously.

9. V

Havg

can be measured directly using “Vtop” on Agilent and “High” on Tektronix oscilloscopes.

10. For V

IN

between 0 V and V

H

ΔV

CROSS

is defined as the total variation of all crossing voltages as defined in note 2.

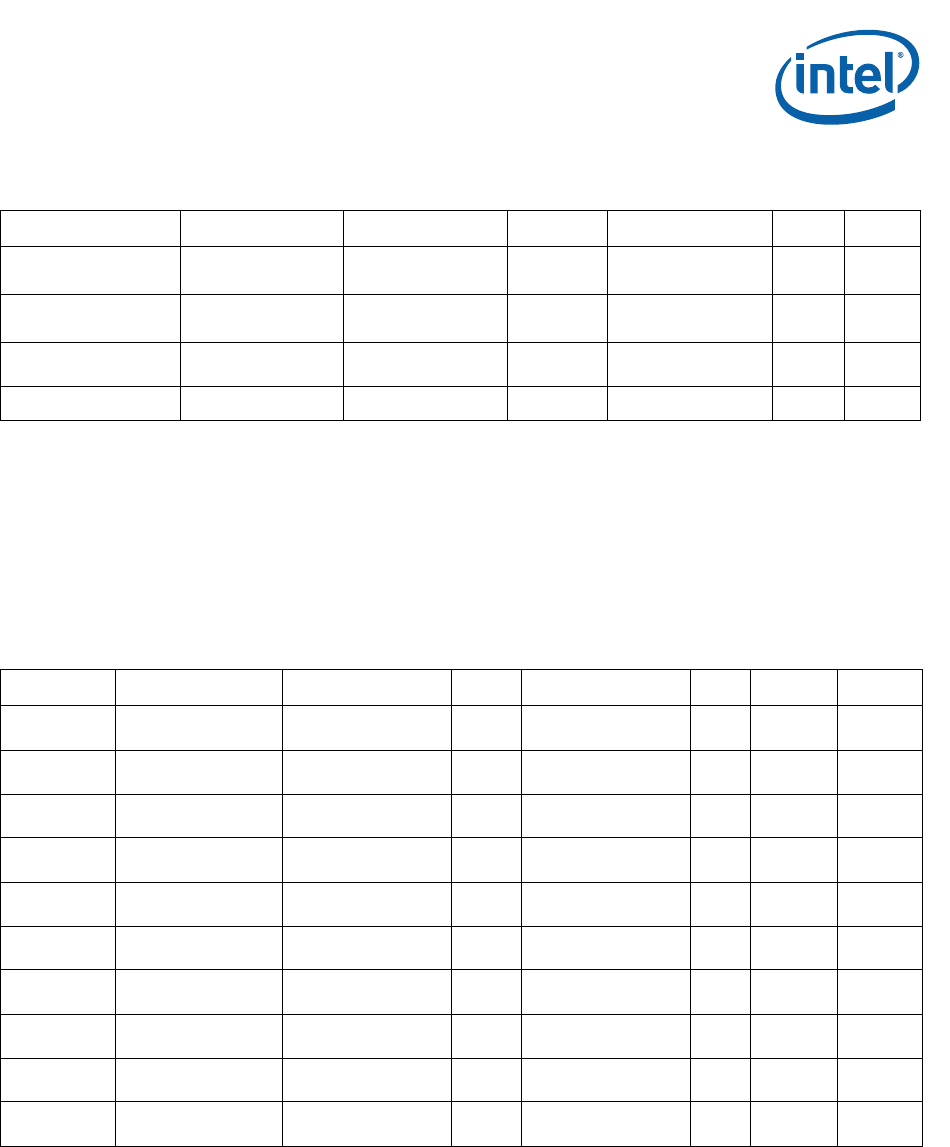

Table 2-17. AGTL+ Bus Voltage Definitions

Symbol Parameter Min Typ Max Units Notes

1

GTLREF_DATA_MID

GTLREF_DATA_END

Data Bus Reference

Voltage

0.98 * 0.67 * V

TT

0.67 * V

TT

1.02 * 0.67 * V

TT

V2, 3

GTLREF_ADD_MID

GTLREF_ADD_END

Address Bus

Reference Voltage

0.98 * 0.67 * V

TT

0.67 * V

TT

1.02 * 0.67 * V

TT

V2, 3

R

TT

Termination

Resistance (pull up)

45 50 55

Ω

4

COMP COMP Resistance 49.4 49.9 50.4

Ω

5

Table 2-18. FSB Differential BCLK Specifications

Symbol Parameter Min Typ Max Unit Figure Notes

1,2

V

IL

Single-ended Input

Low Voltage

-0.150 0.0 0.15 V 2-13

V

IH

Single-ended Input

High Voltage

0.660 0.710 0.850 V 2-13

V

CROSS(abs)

Absolute Crossing

Point

0.250 0.350 0.550 V 2-13,

2-14

2,8

V

CROSS(rel)

Relative Crossing

Point

0.250 +

0.5 * (V

Havg

- 0.700)

N/A 0.550 +

0.5 * (V

Havg

- 0.700)

V 2-13,

2-14

3,8,9, 11

Δ V

CROSS

Vcross variation N/A N/A 0.140 V 2-13,

2-14

V

MAX (Absolute

Overshoot)

Single-ended

maximum voltage

N/A N/A 1.15 V 2-13 4

V

MIN (Absolute

Undershoot)

Single-ended

minimum voltage

-0.300 N/A N/A V 2-13 5

V

RBM

Single-ended

Ringback Margin

0.200 N/A N/A V 2-13 6

V

TR

Single-ended

Threshold Region

V

CROSS

- 0.100 N/A V

CROSS

+ 0.100 V 2-13 7

I

LI

Input Leakage

Current

N/A N/A +/- 100 μA10

- Processor 7200 Series 1

- Contents 3

- 4 Document Number: 318080-002 4

- Document Number: 318080-002 5 5

- 6 Document Number: 318080-002 6

- Document Number: 318080-002 7 7

- Revision History 8

- 1 Introduction 9

- 1.1 Terminology 11

- Introduction 12

- 1.2 State of Data 13

- 1.3 References 13

- 2 Electrical Specifications 15

- Clocking 16

- 2.3.2 PLL Power Supply 17

- Electrical Specifications 18

- Table 2-4. FSB Signal Groups 21

- Asynchronous Signals 22

- 2.9 Mixing Processors 23

- CC_VTT_OUT 27

- Time Duration (s) 28

- Sustained Current (A) 28

- Table 2-10. V 30

- Load Lines 32

- Static and Transient 34

- Tolerance Load Lines 34

- Specifications 35

- 2.11.2.1 DC Characteristics 36

- 2.11.3 V 37

- Overshoot Specification 37

- Example Overshoot Waveform 38

- Tp = T1: BCLK[1:0] period 47

- THERMTRIP# 51

- Figure 2-26. VID Step Timings 54

- 3 Mechanical Specifications 57

- Mechanical Specifications 58

- 3.7 Processor Materials 67

- 3.8 Processor Markings 68

- Processor 69

- 4 Pin Listing 71

- 10 of 16) 75

- 11 of 16) 76

- 12 of 16) 76

- 13 of 16) 77

- 14 of 16) 77

- 15 of 16) 78

- 16 of 16) 78

- 1 of 14) 79

- 2 of 14) 79

- 3 of 14) 80

- 4 of 14) 80

- 5 of 14) 81

- 6 of 14) 81

- 8 of 14) 82

- 7 of 14) 82

- 9 of 14) 83

- 10 of 14) 83

- 11 of 14) 84

- 12 of 14) 84

- 13 of 14) 85

- 14 of 14) 85

- Pin Listing 86

- 5 Signal Definitions 87

- CC and BCLK have reached 92

- 6 Thermal Specifications 95

- CASE_MAX 96

- Thermal Profile 98

- = 0.162 x Power + 45 98

- Pow er (W) 100

- Temperature (C) 100

- = 0.420 x Power + 45 100

- = 0.238 x Power + 45 101

- 6.1.2 Thermal Metrology 102

- 6.2.2 Thermal Monitor 103

- 6.2.3 Thermal Monitor 2 104

- 6.2.4 On-Demand Mode 105

- 6.2.5 PROCHOT# Signal 106

- 6.2.6 FORCEPR# Signal 106

- 6.2.7 THERMTRIP# Signal 106

- 6.3.1 Introduction 107

- 6.3.2 PECI Specifications 108

- 7 Features 111

- 7.2.1 Normal State 112

- EXTENDED_HALT 113

- 7.2.3 Stop-Grant State 114

- 7.3 Enhanced Intel SpeedStep 115

- Technology 115

- Features 116

- 7.4.1 SMBus Device Addressing 117

- Transactions 118

- 7.4.3.1 Header 121

- 7.4.3.2 Processor Data 125

- 7.4.3.3 Processor Core Data 126

- 16h-19h 127

- 1Ah-1Bh 127

- Offset: 1Ch 128

- 1Dh-1Eh 128

- 1Fh-20h 128

- 7.4.3.4 Cache Data 129

- 7.4.3.5 Package Data 131

- 7.4.3.6 Part Number Data 132

- 38h-3Eh 133

- 3Fh-4Ch 133

- 4Dh=54h 133

- 55h-6Eh 134

- 71h-72h 134

- 7.4.3.8 Feature Data 135

- 7.4.3.9 Other Data 136

- 7.4.4 Checksums 137

- 7.4.5 Scratch EEPROM 137

- 8.1 Introduction 139

- 8.2 Thermal Specifications 139

- 9 Debug Tools Specifications 141

- Debug Tools Specifications 142

(102 Seiten)

(102 Seiten)

Kommentare zu diesen Handbüchern