Lenovo 59P5107 Datenblatt Seite 81

- Seite / 102

- Inhaltsverzeichnis

- LESEZEICHEN

Bewertet. / 5. Basierend auf Kundenbewertungen

Low Voltage Intel

®

Xeon

™

Processor at 1.60 GHz, 2.0 GHz and 2.4 GHz

Datasheet 81

BR0#

BR[1:3]#

I/O

I

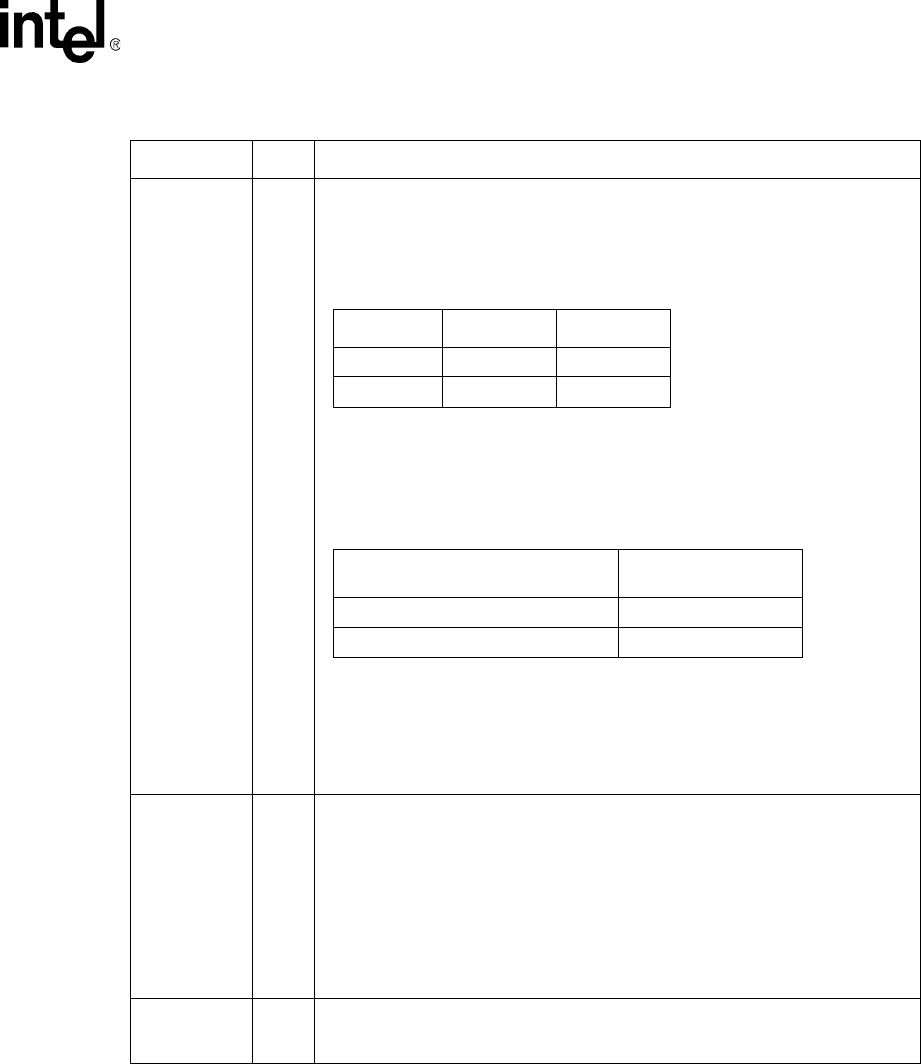

BR[3:0]# (Bus Request) drive the BREQ[3:0]# signals in the system. The

BREQ[3:0]# signals are interconnected in a rotating manner to individual processor

pins. BR2# and BR3# must not be utilized in a dual processor platform design. The

table below gives the rotating interconnect between the processor and bus signals

for dual processor systems.

During power-on configuration, the central agent must assert the BR0# bus signal.

All symmetric agents sample their BR[3:0]# pins on the active-to-inactive transition

of RESET#. The pin which the agent samples asserted determines it’s agent ID.

These signals do not have on-die termination and must be terminated at the

end agent. See the appropriate platform design guidelines for additional

information.

BSEL[1:0]

O

These output signals are used to select the system bus frequency.

A BSEL[1:0] = 00 will select a 100 MHz bus clock frequency. The frequency is

determined by the processor(s), chipset, and frequency synthesizer capabilities. All

system bus agents must operate at the same frequency. Individual processors will

only operate at their specified front side bus (FSB) frequency.

On baseboards which support operation only at 100 MHz bus clocks these signals

may be ignored. On baseboards employing the use of these signals, a 1 K

Ω pull-up

resistor be used.

See Table 3, “System Bus Clock Frequency Select Truth Table for BSEL[1:0]” on

page 15 for output values.

COMP[1:0] I

COMP[1:0] must be terminated to V

SS

on the baseboard using precision resistors.

These inputs configure the AGTL+ drivers of the processor. Refer to the appropriate

platform design guidelines and Table 12 for implementation details.

Table 36. Signal Definitions (Sheet 3 of 9)

Name Type Description

BR[1:0]# Signals Rotating Interconnect, dual processor system

During power-up configuration, the central agent must assert the BR0# bus sign

al.

All symmetric agents sample their BR[1:0]# pins on active-to-inactive transition o

f

RESET#. The pin on which the agent samples an active level determines its age

nt

ID. All agents then configure their pins to match the appropriate bus signal proto

col

as shown below.

Bus Signal Agent 0 Pins Agent 1 Pins

BREQ0# BR0# BR1#

BREQ1# BR1# BR0#

BR[1:0]# Signal Agent IDs

BR[1:0]# Signals Rotating

Interconnect, dual processor system

Agent ID

BR0# 0

BR1# 1

- Low Voltage Intel 1

- Processor at 1

- 1.60 GHz, 2.0 GHz and 2.4 GHz 1

- 2 Datasheet 2

- Contents 3

- Revision History 7

- 8 Datasheet 8

- 1.0 Introduction 9

- 1.1 Terminology 10

- 1.2 State of Data 11

- 1.3 References 11

- 12 Datasheet 12

- 2.0 Electrical Specifications 13

- Decoupling 14

- 2.5 PLL Filter 15

- Figure 1. Typical V 16

- Power Distribution 16

- 2.6 Voltage Identification 17

- 18 Datasheet 18

- 2.7 Reserved Or Unused Pins 19

- 2.8 System Bus Signal Groups 19

- 20 Datasheet 20

- 2.9 Asynchronous GTL+ Signals 21

- 2.10 Maximum Ratings 21

- 22 Datasheet 22

- Datasheet 23 23

- Figure 3. Low Voltage Intel 24

- Processor Voltage and 24

- Datasheet 25 25

- 26 Datasheet 26

- Datasheet 27 27

- 28 Datasheet 28

- Datasheet 29 29

- 30 Datasheet 30

- Datasheet 31 31

- 32 Datasheet 32

- Datasheet 33 33

- 34 Datasheet 34

- Datasheet 35 35

- 36 Datasheet 36

- Figure 15. THERMTRIP# to V 37

- Power Down 38

- Power Up 38

- Datasheet 39 39

- 40 Datasheet 40

- Noise Margi 41

- 42 Datasheet 42

- Datasheet 43 43

- 3.3.4 Activity Factor 44

- Specifications 45

- 46 Datasheet 46

- Datasheet 47 47

- 48 Datasheet 48

- Undershoot Tolerance 49

- 50 Datasheet 50

- 4.0 Mechanical Specifications 51

- 4.1 Mechanical Specifications 52

- Figure 25. Low Voltage Intel 53

- 54 Datasheet 54

- Datasheet 55 55

- 56 Datasheet 56

- 4.3 Insertion Specifications 57

- 4.4 Mass Specifications 57

- 4.5 Materials 57

- 4.6 Markings 58

- 4.7 Processor Pin-Out Diagram 58

- Datasheet 59 59

- 60 Datasheet 60

- 5.1 Processor Pin Assignments 61

- 62 Datasheet 62

- Datasheet 63 63

- 64 Datasheet 64

- Datasheet 65 65

- 66 Datasheet 66

- Datasheet 67 67

- 68 Datasheet 68

- Datasheet 69 69

- 70 Datasheet 70

- Datasheet 71 71

- 72 Datasheet 72

- Datasheet 73 73

- 74 Datasheet 74

- Datasheet 75 75

- 76 Datasheet 76

- Datasheet 77 77

- 78 Datasheet 78

- 5.2 Signal Definitions 79

- 80 Datasheet 80

- 82 Datasheet 82

- Datasheet 83 83

- 84 Datasheet 84

- Datasheet 85 85

- 86 Datasheet 86

- Datasheet 87 87

- 88 Datasheet 88

- 6.0 Thermal Specifications 89

- 90 Datasheet 90

- Datasheet 91 91

- 92 Datasheet 92

- 7.0 Features 93

- 94 Datasheet 94

- 7.2.5 Sleep State—State 5 95

- 7.3 Thermal Monitor 96

- 7.4 Thermal Diode 97

- 98 Datasheet 98

- Debug Port Design Guide 99

- 100 Datasheet 100

- 9.0 Appendix A 101

- 102 Datasheet 102

(136 Seiten)

(136 Seiten)

(12 pages)

(12 pages)

Kommentare zu diesen Handbüchern